即便 DDR5 预计在今年夏天,才会由 JEDEC 公布最后正式规范,但是相关厂商早已等不及,利用接近完工的草案版本进行设计量产测试。著名的电子设计自动化公司 Cadence 与 Micron 合作测试第一款可实际运作的 DDR5 控制器与内存颗粒,并使用台积电 7 奈米制程制造。

JEDEC 预计今年夏天即可推出下一世代动态内存 DDR5 正式规范,但是前期设计与测试验证已如火如荼进行。电子设计自动化公司 Cadence 与 Micron 合作,在实验室开发出第一款确实运作的 DDR5 内存设备,包含控制器、实体层、内存颗粒,内存颗粒为美光设计制造,并由台积电 7 奈米制程产出。

这款实际可运作的 DDR5 平台实际运作速度为 4,400MT/s,相比 DDR4-3200 快上许多,但 Cadence 部落格文章提到,DDR5 相对 DDR4 而言依然以增加容量为主,利用如垂直堆叠方式让制造 16Gb 颗粒更容易,核心内存运作方式相较过去没有太大变化,同样使用外部 I/O 提升传输速度。DDR5 规格预计将从 4,400MT/s 开始,直至 6,400MT/s,预计今年底或明年初有少部分产品开始使用。

▲ 近期 DDR 内存进展时程。

DDR5 相对于 DDR4 内存,除了外部 I/O 传输速度提升,电压预期将从 +1.2V 降低至 +1.1V,上拉 VDDQ 设计也会从资料总线进一步扩展至位址总线。此外由于处理器 Socket、内存布线过长、量产电路板瑕疵、空内存模组槽位等不利于讯号传输完整性因素,DDR5 在控制器端资料总线也会导入 FFE(Feed-Forward Equalization)、CTLE(Continuous Time Linear Equalization)、DFE(Decision Feedback Equalization)等化器技术改善讯号传输品质,而 DFE 也会加入至内存模组的资料总线。

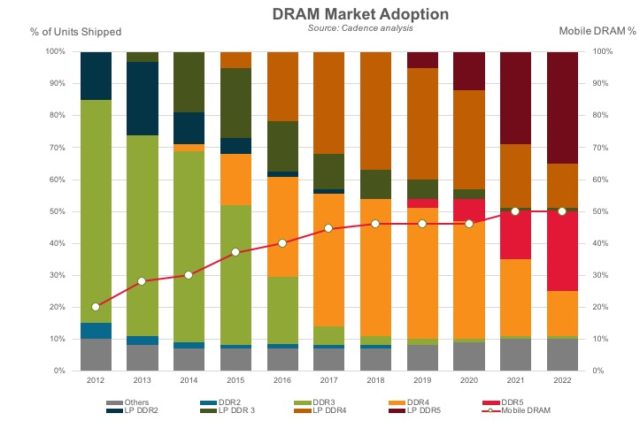

▲ 动态内存市场变化趋势图。(Source:Cadence)

- DDR5 IP Test Chip Operates with Micron Prototype DRAM at 4400 MT/s

(本文由 T客邦 授权转载;首图来源:美光)