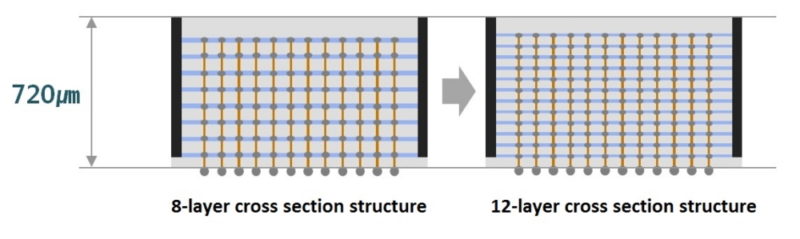

三星电子宣布,开发出业界首见的 12 层 3D 硅穿孔技术(Through-Silicon Via,简称 TSV)。DRAM 芯片的堆叠层数能从 8 层增至 12 层,不久后将量产 24GB 的高带宽内存(HBM)。

三星新闻稿指出,12 层 3D-TSV 技术,被视为量产高效能芯片最具挑战的封装技术之一,需要极度精准,才能让 12 层 DRAM 芯片,透过 6 万个 TSV 穿孔的 3D 结构,垂直互连,厚度只有人类头发的二十分之一。

(Source:三星)

采用这个封装技术的产品,厚度为 720 微米,与当前 8 层的二代高带宽内存相同。这是零组件设计的重大进展,客户可以推出新一代的大容量、高效能产品,却毋须更动系统结构设计。不只如此,和现行的打线接合(wire bonding)技术相比,3D 封装能缩短芯片间的数据传输时间,可提高速度、减少耗电。

三星电子的测试与系统封装执行副总 Hong-Joo Baek 说,摩尔定律濒临界线,预料 3D-TSV 技术将益发重要,希望成为此先进封装技术的要角。

(本文由 MoneyDJ新闻 授权转载;首图来源:shutterstock)